Аппаратно-программный

комплекс для моделирования и реализации цифровых устройств и систем управления

И.В. Коновалов,

вед. инж. лаб. 18 ivan-k85@mail.ru,

ИПУ РАН, г. Москва

В.Н. Коновалов,

ст. препод., v.konovalov@list.ru,

КФ МГТУ им. Н.Э. Баумана, г. Калуга

В статье

рассматривается универсальное многофункциональное лабораторное оборудование на

основе микросхем программируемой логики и микроконтроллеров, используемое для

подготовки инженерных кадров.

Multipurpose

educational equipment for engineers training built on complex programmable

logic devices and microcontrollers is considered.

Интересы России требуют преодоления сложившегося в

последние годы однобокого развития экономики с акцентом на сырьевые отрасли

производства. Неотъемлемой чертой развитых государств является способность к

разработке и производству изделий высоких технологий, среди которых одно из

ведущих мест занимает электронная аппаратура. Успех электроники в значительной

мере определяет технологический прогресс многих отраслей промышленности.

Высокий уровень развития

системы образования и качественные показатели обучения стоят в одном ряду с

важнейшими факторами, обеспечивающими устойчивое и поступательное

социально-экономическое развитие страны, её конкурентоспособность и

безопасность в современном мире. Создание и применение новых знаний в реальной

жизни становятся основным источником роста национальной экономики и

благосостояния российского народа.

Эффективная

передача знании й обучаемым возможна только при обеспечении учебного процесса

всеми необходимыми средствами обучения. Для реализации такого подхода к

процессу обучения необходимо не только стандартное лабораторное оборудование, а

целый учебно-методический комплекс, который представляет собой комплект самостоятельных,

взаимодополняющих средств обучения, позволяющий передавать обучаемым не только

теоретические знания, но и прививать им практические навыки работы в области

будущей производственной деятельности. Технические, программные и методические

средства позволяют задействовать у обучаемых все каналы восприятия передаваемой

им информации, что значительно повышает эффективность ее усвоения.

При изучении

цифровой электроники, как правило, возникает проблема практической реализации и

испытания изучаемых схем и устройств. В настоящее время существует большое

количество устройств, предназначенных для указанных целей. Однако, выпускаемые

отечественными и зарубежными фирмами отладочные платы и стартовые наборы на

основе микросхем программируемой логики

и микроконтроллеров, как правило, представляют собой печатные платы, содержащие

минимальный набор необходимых периферийных устройств и макетное поле, на

котором возможно однократное размещение дополнительных элементов схемы. Такой

подход направлен на быстрое проектирование и отладку необходимых схемотехнических

и программных решений при создании новых устройств, что в корне противоречит

учебным задачам. Для реализации процесса обучения необходимо, чтобы достаточно

большой набор периферийных устройств уже был размещён на плате стенда с возможностью

быстрого подключения/отключения указанных устройств в процессе проектирования и

отладки новых схем.

Целью данной

научно-исследовательской работы является разработка универсального современного

лабораторного оборудования для подготовки высококвалифицированных

инженерных кадров в области автоматизации технологических процессов и

производств, информационных технологий, вычислительной техники, электроники и

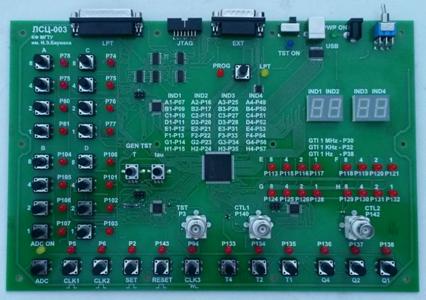

микроэлектроники. Разработанные в Калужском филиале МГТУ им. Н.Э Баумана

лабораторные стенды ЛСЦ-003 и МКС-003 предназначены для автоматизированного

проектирования, построения, отладки и демонстрации широкого спектра цифровых устройств

и систем управления в учебных задачах различного содержания и степени

сложности. Предлагаемая к реализации структура

лабораторных стендов включает все необходимые для проведения практических

занятий элементы – блоки формирования входных сигналов, блоки индикации и

контроля выходных сигналов, интерфейсные блоки для подключения к персональному компьютеру

(ПК), блок сопряжения с внешними устройствами, блок программирования и

универсальный блок питания.

Структурная схема стенда ЛСЦ-003

Структурная схема стенда ЛСЦ-003 представлена на

рис.1.

Основным элементом конструкции стенда,

непосредственно предназначенным для физической реализации цифровых схем,

является программируемая логическая интегральная схема (ПЛИС) фирмы Xilinx

xc95288xl. Указанная ПЛИС построена на основе архитектуры CPLD (Complex Programmable Logic Device),

содержит в своей структуре 288 макроячеек (6 400 эквивалентных логических

вентилей), что позволяют реализовывать на её основе широкий спектр цифровых

устройств и систем без использования дополнительных элементов (например,

внешних ПЗУ для хранения конфигурационных последовательностей) [1].

Для подачи на исследуемую цифровую схему входных

воздействий в стенд включены блоки формирования входных сигналов БФВС1, БФВС2 и

БФВС3, позволяющие генерировать статические (A, B, C, D, T, Q) и динамические

(импульсные) (C1, C2, SET, RESET) логические сигналы.

Уровни указанных сигналов можно наблюдать визуально на дискретных светодиодных

индикаторах. Кроме того блоки БФВС позволяют формировать сетку опорных тактовых

сигналов (ТИ1, ТИ2, ТИ3) с частотами 1 МГц, 1 КГц и 1 Гц,

которые в случае необходимости могут использоваться для синхронизации и

тактирования исследуемых цифровых схем.

рис.1 Структурная схема

стенда ЛСЦ-003

Блок БФВС2 может работать в режиме

аналогово-цифрового преобразователя (АЦП), при этом на его выходах формируется цифровой

код, соответствующий величине входного напряжения VIN, поступающего с блока

сопряжения с внешними устройствами (БСВУ).

Блок БФВС3 имеет входной разъем ГИ для подключения

внешнего генератора с целью подачи на исследуемую схему импульсных сигналов TST.

Блок сопряжения с внешними устройствами (БСВУ)

позволяет подключить к стенду ЛСЦ-003 дополнительные элементы (двигатели

постоянного тока, вентильные и шаговые двигатели, электромеханические

исполнительные устройства, различные датчики и др.), которые могут

потребоваться для моделирования и реализации сложных систем автоматического

управления. Для управления мощными исполнительными устройствами необходимо

использовать внешние усилительные и ключевые элементы.

Блок индикации БИ7-4 представляет собой четыре

сдвоенных семисегментных индикатора со статическим управлением, которые

позволяют наблюдать состояния на выходах исследуемых схем в виде изображения

шестнадцатеричных или десятичных цифр. При этом дешифратор для управления

индикаторами должен быть реализован средствами ПЛИС.

Блок индикации и контроля БИК представляет собой 16

дискретных светодиодов, которые позволяют визуально наблюдать состояния на

соответствующих выводах ПЛИС. Кроме того, в состав блока БИК входят два разъема

CTL1 и CTL2, к которым может быть подключен двухлучевой осциллограф OSC для

наблюдения динамических (импульсных) сигналов. Для подключения выходов CTL1 и

CTL2 к различным внутренним точкам исследуемых схем можно использовать

мультиплексоры, входящие в структуру ПЛИС. Такой подход позволяет

контролировать статические и динамические сигналы на выходах сложных цифровых

устройств и систем.

Блок интерфейса USB БИ USB построен на основе специализированной микросхемы FT245BM, преобразующей

сигналы шины USB в восьмиразрядный параллельный интерфейс,

представленный однобайтным портом шины данных и сигналами управления и

синхронизации. Выводы параллельного порта и управляющие сигналы подключены к

выводам ПЛИС.

Блок интерфейса LPT БИ LPT обеспечивает сопряжение персонального компьютера (ПК) со

стендом ЛСЦ-003. При этом все сигналы стандартного LPT-порта ПК подаются на выводы ПЛИС.

Указанные интерфейсные блоки обеспечивают возможность

передачи данных между ПК и реализованным на ПЛИС устройством с целью проведения

его автоматизированного тестирования или реализации автоматических цифровых

систем с ЭВМ в контуре управления.

Блок программирования БПР построен на основе буферных

элементов sn74ls125 и может совместно с блоком БИ LPT работать в одном из двух задаваемых пользователем режимов:

1. «ПРОГРАММИРОВАНИЕ». В этом режиме

обеспечивается передача конфигурационных файлов из ПК в ПЛИС с использованием

сигналов TMS, TCK, TDI и TDO интерфейса JTAG. Такие файлы

формируются на этапе проектирования цифровых устройств специализированными

средствами САПР (например, пакетом WebPACK ISE для ПЛИС фирмы Xilinx);

2. «ИНТЕРФЕЙС». В этом режиме

обеспечивается непосредственное подключение сигналов LPT-порта к выводам ПЛИС для

сопряжения исследуемых цифровых устройств с ПК.

Блок питания БП реализован на микросхемах LM1117 и служит для получения стабилизированных напряжений

+5 В (VCC5A и VCC5B) и +3,3 В (VCC3.3) для

питания стенда. Входное напряжение VPOW подается от

внешнего нестабилизированного источника постоянного тока, имеющего на выходе

напряжение 7 … 8 В при токе нагрузки 0,8 … 1 А.

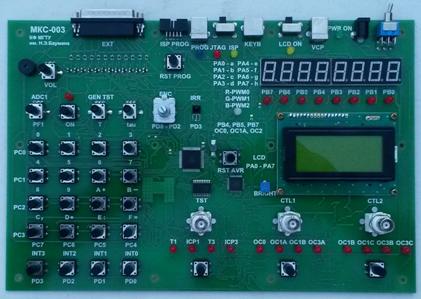

Структурная схема стенда МКС-003

Структурная схема стенда

МКС-003 представлена на рис.2. Основным элементом конструкции стенда,

непосредственно предназначенным для физической реализации цифровых схем

управления, является микроконтроллер AVR ATmega128, который представляет собой 8-разрядный RISC-микроконтроллер

общего назначения с быстрым процессорным ядром. Ядро микроконтроллеров AVR,

выполненное по усовершенствованной RISC-архитектуре (enhanced RISC – Reduced Instruction Set Computer) сочетает богатый набор инструкций с 32 универсальными рабочими регистрами

(РОН). Арифметико-логическое устройство (АЛУ), выполняющее все вычисления,

подключено непосредственно к 32-м рабочим регистрам, объединенным в регистровый

файл. Благодаря этому АЛУ выполняет одну операцию (чтение содержимого

регистров, выполнение операции и запись результата обратно в регистровый файл)

за один машинный цикл [2].

рис.2

Структурная схема стенда МКС-003

В микроконтроллерах AVR реализована

Гарвардская архитектура, которая характеризуется использованием раздельной

памяти программ (типа Flash) и памяти данных (типов SRAM и EEPROM), каждая из

которых имеет собственные шины доступа к ним. Такая организация позволяет

одновременно работать как с памятью программ, так и с памятью данных.

Разделение шин доступа позволяет использовать для каждого типа памяти шины

различной разрядности, причем способы адресации и доступа к каждому типу памяти

также различны. Такое построение кристалла обеспечивает существенное повышение

производительности, которая в пределе позволяет достигать значения 1MIPS (1 млн. операций в секунду) на 1МГц тактовой

частоты процессора, что позволяет

проектировщикам систем оптимизировать соотношение энергопотребления и быстродействия.

Для

разработки и отладки программ для микроконтроллеров AVR используются специальные пакеты, такие как AVR Studio или Code Vision AVR, которые позволяют подготовить и отладить соответствующую

программу на персональном компьютере, а затем загрузить ее в память

микроконтроллера с использованием технологии внутрисхемного программирования.

Такой подход значительно облегчает процесс проектирования и отладки прикладного

программного обеспечения и сокращает сроки разработки цифровых устройств.

Описанные выше особенности

микроконтроллеров AVR, к которым относится ATmega128,

позволяют реализовывать на их основе широкий спектр цифровых устройств и

систем управления.

Блок оперативного

запоминающего устройства БОЗУ служит для увеличения емкости памяти данных,

расположенной внутри кристалла ATmega128 (4 Кбайт), до 36 Кбайт и содержит в

своем составе регистр адреса, реализованный на микросхеме SN74HC573,

и микросхему внешнего статического ОЗУ UT62256 (32 К х 8 бит).

Блок кнопочной клавиатуры

БКЛВ является типовым устройством ввода информации микропроцессорных систем и

содержит в своем составе 16 кнопок 0, 1, 2 … F, организованных в матрицу

размером 4 х 4 и подключенных к порту С, и 4 кнопки INT0 … INT3,

подключенные к соответствующим входам внешних прерываний.

Блок управления подачей

тестовых сигналов БУ TST служит для формирования тестовых импульсных сигналов с

изменяемыми параметрами (период повторения и длительность импульсов) и их

подачи на один из входов T1, ICP1, T3 и ICP3

таймеров счетчиков МК ATmega128 с целью измерения

параметров указанных сигналов. Кроме того, имеется возможность подачи сигналов

на вход TST от внешнего импульсного генератора.

Блок периферийных устройств

БПУ содержит в своем составе ряд типовых внешних устройств, широко используемых

в микропроцессорных системах для ввода/вывода информации:

- интегральный модуль

инфракрасного приемника сигналов от телевизионного пульта дистанционного

управления (с несущей частотой 36 КГц);

- энкодер;

- потенциометр, подключенный

к входу ADC1 аналого-цифрового преобразователя;

- динамический

громкоговоритель, подключенный к выходу OC1A таймера T1 для формирования

звуковых сигналов;

- входной разъем KEYB

для подключения к стенду стандартной клавиатуры PS/2 от персонального

компьютера. К указанному разъему могут быть подключены и другие внешние

устройства, например цифровой датчик температуры DS1820.

Блок интерфейса

виртуального COM-порта БИ VCP реализован на основе специализированной микросхемы FT232RL,

преобразующей сигналы RX0 и TX0 модуля USART0 МК ATmega128 в сигналы USBDP и

USBDM, и служит для передачи данных между стендом МКС-003 и USB-портом

ПК, что обеспечивает возможность построения распределенных автоматизированных

измерительных и управляющих систем.

Блок программирования БПР реализован на МК ATmega16 и интерфейсной микросхеме

FT232RL и служит для загрузки в стенд hex-файла скомпилированной

программы. Блок БПР подключается к USB-порту ПК и может работать в одном из двух задаваемых пользователем режимов:

1. «JTAG». В этом режиме обеспечивается

совместимость с программатором JTAG ICE II, что позволяет осуществлять загрузку

и отладку прикладной программы из пакета AVR Studio 4.19 с использованием

интерфейса JTAG;

2. «ISP». В этом режиме

обеспечивается возможность загрузки прикладной программы в стенд с

использованием интерфейса SPI.

Блок сопряжения с внешними

устройствами БСВУ позволяет подключить к стенду МКС-003 дополнительные элементы

(двигатели постоянного тока, вентильные и шаговые двигатели,

электромеханические исполнительные устройства, различные датчики и др.),

которые могут потребоваться для моделирования и реализации сложных систем

автоматического управления. Для управления мощными исполнительными устройствами

необходимо использовать внешние усилительные и ключевые элементы.

Блок аналогового

ввода/вывода БАВВ включает в себя входной измерительный усилитель, подключенный

к входу ADC0 МК ATmega128, и цифро-аналоговый преобразователь DAC7513 с

выходным усилителем, подключенный к выводам интерфейса SPI МК ATmega128. Блок

БАВВ обеспечивает возможность работы стенда МКС-003 с аналоговыми сигналами в

диапазоне – 2,56 В … + 2,56 В.

Блок индикации БИ LED

служит для вывода информации и включает 8-разрядный семисегментный светодиодный

индикатор со схемами управления, работающий в режиме динамической индикации, а

так же восемь отдельных светодиодов, подключенных непосредственно к выводам

порта B МК ATmega128. Кроме того, в состав

рассматриваемого блока входит двухцветный (красно-зеленый) светодиод, выводы которого

подключены к выходам таймеров T0 и T2 МК ATmega128.

Блок индикации БИ LCD

реализован на основе стандартного 2х- или 4х-строчного жидкокристаллического

индикатора и служит для вывода алфавитно-цифровой информации. Имеется

возможность включения/отключения подсветки экрана индикатора и регулировки

контрастности изображения.

Блок управления выходами

контроля БУ CTL имеет в своем составе два разъема CTL1 и CTL2, к которым может

быть подключен двухлучевой осциллограф OSC для наблюдения импульсных

выходных сигналов таймеров T0, T1 и T3 МК ATmega128.

Блок питания БП реализован на специализированных микросхемах

LM1117 и ICL7660 и служит для получения стабилизированных напряжений +5 В

(VCC5A и VCC5B) для питания цифровых устройств стенда МКС-003, +5 В (AVCC) и –5 В (AVDD) для питания аналоговых устройств. Кроме

того, в состав блока БП входит формирователь опорного напряжения +2,56 В

(AREF), реализованный на микросхеме TL431. Входное напряжение VPOW подается от внешнего нестабилизированного источника

постоянного тока, имеющего на выходе напряжение 7 … 8 В при токе

нагрузки 0,5 … 0,8 А.

Учебная САПР Decomposer на основе методов многоуровневой декомпозиции

Разработка и проектирование современных цифровых устройств

невозможны без применения систем автоматизированного проектирования (САПР).

Практически все программы САПР, применяющиеся в настоящее время на предприятиях

и в учебных заведениях, разработаны зарубежными фирмами и являются платными.

Кроме того, алгоритмы синтеза цифровых устройств, применяющиеся в указанных

программах, как правило, не афишируются. Обучение студентов в таких условиях

сводится лишь к освоению существующего программного обеспечения и не позволяет

готовить высококвалифицированных специалистов, способных решать сложные

творческие задачи. Разработанная в Калужском филиале МГТУ им. Н.Э. Баумана

учебная САПР Decomposer основана на

открытых алгоритмах многоуровневой декомпозиции и позволяет

эффективно решать многовариантные задачи логического синтеза цифровых устройств

и выбирать наиболее приемлемое техническое решение, что является необходимой

составляющей процесса обучения.

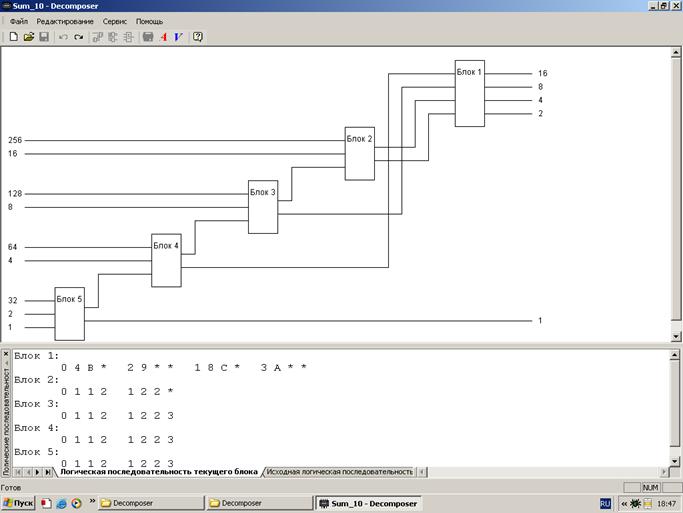

рис.

3 Главное окно программы Decomposer

Пакет

написан на языке C++,

имеет развитый графический пользовательский интерфейс и обеспечивает выполнение

следующих функций [3]:

- задание

числовой (логической) последовательности синтезируемой схемы;

- проведение

параллельной и последовательной декомпозиции схемы;

- проведение

детализации схемы до уровня двухвходовых блоков;

- анализ

синтезированной схемы на соответствие исходному описанию;

- трансляция

схемы в описание на языке VHDL,

что даёт

возможность интегрироваться в специализированные пакеты программ (например, WebPACK ISE) с целью получения файлов для «прошивки» микросхем

программируемой логики и практической реализации спроектированного цифрового устройства,

например, на стенде ЛСЦ-003.

Синтезируемая

схема (в данном случае это двоично-десятичный сумматор) в графическом виде

изображается в рабочем окне программы, а в окне отчёта приводятся имена блоков

и соответствующие им числовые последовательности (рис 3).

Широкие функциональные

возможности программного пакета Decomposer и лабораторного стенда

ЛСЦ-003 позволяют проводить полный цикл автоматизированного проектирования

цифровых устройств от исходного описания до физической реализации спроектированной

схемы на ПЛИС. Пакет внедрен в учебный процесс в Калужском филиале МГТУ им.

Н.Э. Баумана и используется при подготовке высококвалифицированных инженерных

кадров. Авторами получено

свидетельство № 2007611828

об официальной регистрации пакета в Реестре программ для ЭВМ.

Конструкция

лабораторных стендов ЛСЦ-003 и МКС-003

Конструктивно стенды

выполнены в виде двухсторонней печатной платы размером 200 х

Плата может использоваться в варианте без корпуса. В этом

случае к ее нижней стороне следует прикрепить пластиковые или резиновые ножки,

обеспечивающие устойчивое расположение стенда на рабочем столе.

В случае необходимости обеспечения повышенной защиты от

внешних механических воздействий, плата может быть помещена в корпус из пластика

или листового металла с прозрачной верхней панелью, через отверстия в которой

осуществляется нажатие тактовых кнопок.

Альтернативным вариантом

полномасштабного (и сложного в производстве) корпуса может служить корпус типа

«сэндвич», представляющий собой верхнюю (прозрачную) и нижнюю (алюминиевую)

пластины, соединенные с платой посредством монтажных стек. Внешний вид

лабораторных стендов показан на рис. 4.

|

|

|

|

а) |

б) |

рис. 4 Внешний вид лабораторных стендов ЛСЦ-003 (а)

и МКС-003 (б)

Описанные выше

структурные схемы лабораторных стендов ЛСЦ-003 и МКС-003 позволяют решать

учебные задачи различного содержания и степени сложности, связанные с

моделированием отладкой и демонстрацией широкого спектра микропроцессорных измерительных

и управляющих систем.

Работа

над проектом осуществлялась при поддержке Фонда содействия развитию малых форм

предприятий в научно-технической сфере в рамках программы «ПРИОРИТЕТ-2012»

(гос. контракт № 19683).

Литература

1. Кузелин М.О., Кнышев Д.А., Зотов В.Ю. Современные

семейства ПЛИС фирмы Xilinx. Справочное пособие. – М.: Горячая линия–Телеком,

2004. – 440 с.: ил.

2. Евстифеев А.В. Микроконтроллеры AVR семейства Mega.

Руководство пользователя. – М.: Издательский дом «Додэка-XXI», 2007. – 592 с.: ил.

3. САПР Decomposer для

автоматизированного проектирования цифровых схем / В.Н. Коновалов, А.А. Белов,

И.В. Коновалов [и др.] // Системный анализ и информационные технологии САИТ – 2007:

труды второй междунар. конф. – М.: Изд. ЛКИ, 2007. – Т. 2. – С. 270–273.