Разработка

высокочастотных интегрально-гребенчатых фильтров в составе квадратурного

модулятора

на базе технологии 0,18 мкм

В.И.

Сединин,

д.т.н,

проф., sedvi@bk.ru,

СибГУТИ,

г. Новосибирск

В.И.

Мамычев,

инж., mamychev@nzpp,

А.В.

Глухов,

научн.

зам. дир., gluhov@nzpp.ru,

ОАО «НЗПП с ОКБ», г.

Новосибирск

В статье

рассматривается методика проектирования CIC – фильтров 3 порядка для систем

повышенного быстродействия применяемых в DSP по технологии 0.18мкм. Основной упор сделан

на оптимизацию быстродействия, энергопотребления и архитектуры CIC. Рассмотрена

работа в САПР синтеза схемы Design

Compiler (Synopsys) и САПР MATLAB для синтеза HDL-описаний.

В настоящее время квадратурная

цифровая модуляция является одной из самых популярных и надежных типов передачи

информации[5]. Это связано в первую очередь с

возможностью точной подстройки частоты и разности фаз квадратурных и

синфазных составляющих[9]. В данном случае вся неточность вкладывается во

внешний источник тактового сигнала и практически не зависит от погрешностей

технологии, температуры, напряжения питания и т.д. Эти факторы делают цифровые модуляторы более

привлекательными как с точки зрения разработчика, так и с точки зрения потребителя.

При этом для повышения частоты

дискретизации в тракте обработки модулятора используется интерполирующий фильтр

т. к. он обеспечивает наиболее

оптимальное сочетание затраченных ресурсов и полученных характеристик[1].

Прямым аналогом подлежащим

импортозамещению является система на кристалле AD9957 имеющая максимальную

частоту работы 1ГГц и диапазон свободный от паразитных составляющих более

80дБ[11].

Однако, реализация CIC-фильтра на

технологии 0,18 мкм является нетривиальной задачей по следующей основной

причине: технология 0,18 мкм, как правило, используется для систем с

быстродействием ниже 500МГц. Как следствие использование большинства IP-блоков

в проектах требующих более высокое быстродействие не приведет к желаемому

результату. Средствами синтеза эта

проблема также решается с трудом. При использовании стандартных архитектур

оптимизация в САПР синтеза будет предполагать либо конвейерную, либо

мультиплексированную техники повышения быстродействия. При повышении рабочих

частот такой подход становится малоэффективным и кроме того вызывает резкое

повышения энергопотребления схемы в случае с конвейеризацией и повышения

площади кристалла в случае мультиплексирования.

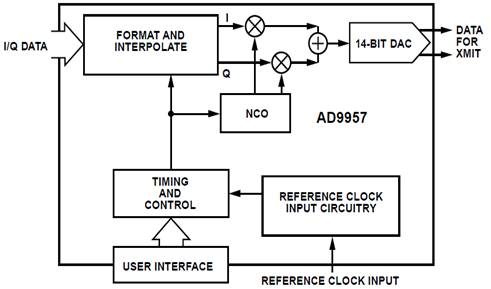

Общая структурная схема квадратурного

модулятора, рассматриваемого в данной статье, приведена на рисунке 1(схема взята

из описания аналога устройства[11]). CIC-фильтр(FORMAT AND INTERPOLATE)

выполняет функцию интерполяции низкочастотного цифрового сигнала[3].

Максимальная частота на выходе

CIC-фильтра может доходить до 1 ГГц.

рис. 1. Общая

структурная схема квадратурного модулятора AD9957-1

Рассмотрим реализацию цифрового

аккумулятора использующегося в CIC. При реализации конвейерным методом на

частотах свыше 1000МГц требуется максимальная степень

конвейеризации т.к. при таких частотах время, отводимое на путь сигнала с

учетом времен предустановки и удержания (см. рисунок 2) составляет менее 500пс.

Среднее время задержки одноразрядного

полного сумматора (0,18 мкм) составляет около 500пс. В результате не более

одного полного сумматора может находиться в пути цифрового сигнала.

рис. 2. Структура

времени цифрового пути для частоты 1ГГц

Зависимость мощности потребления от

разрядности аккумулятора и частоты можно представить в виде:

![]() (1)

(1)

где:

k – постоянная определяющаяся технологическими

параметрами.

f - частота работы аккумулятора.

N - число вентилей в модуле.

В свою очередь N приближено можно

представить как:

![]() (2)

(2)

где w – разрядность аккумулятора.

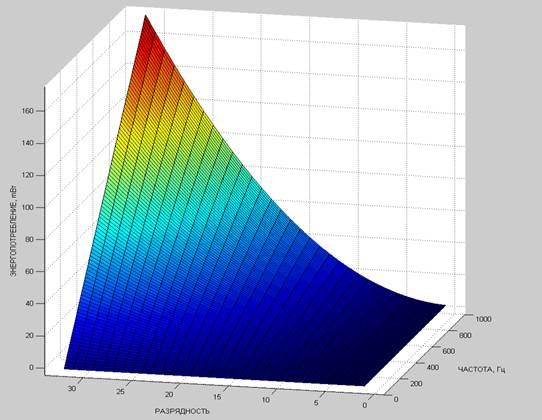

Объединяя (1) и (2) получим

зависимость представленную на рис. 3. Характер зависимости показывает, что при

высокой разрядности слов наблюдается резкое повышение энергопотребления.

рис. 3. 3D-зависимость

энергопотребления конвейерного аккумулятора от частоты и разрядности

Исходя из вышеназванных причин,

реализация CIC требует проработок архитектуры, алгоритма синтеза и

энергопотребления.

СIC-фильтр имеет возможность

программирования и может интерполировать сигнал с коэффициентом от 1 до 63.

Несмотря на свою популярность,

CIC-фильтр имеет сложности реализации по 0.18 мкм технологии в области высоких

частот (свыше 500МГц). Это в первую очередь связано с ограничением

быстродействия стандартных конструкций сумматоров, делителей частоты и т.д. В

первую очередь все сложности связаны с процессом интерполяции. В частности

реализация 32-разрядного CIC-фильтра стандартными блоками (схема быстрого

суммирования) дает максимальную частоту работы не более 100МГц.

В условиях высокого быстродействия

возникает проблема потребления электроэнергии. Особенно эта проблема характерна

для схем использующих конвейерную оптимизацию.

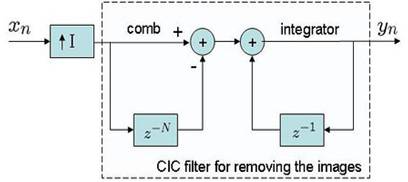

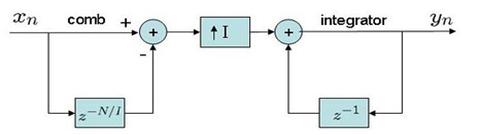

Упрощенная структура СIС-фильтра

представлена на рисунке 4.

рис. 4. Структурная схема

CIC-фильтра в режиме интерполяции

CIC-фильтр состоит из 2 секций: секция

гребенчатых фильтров(comb) и секция интеграторов(integrator). Передаточную

характеристику этого фильтра можно представить в виде[2]:![]()

![]() (3)

(3)

Где N – количество элементов задержки

гребенчатого фильтра.

Поставляя Z = exp(jw) получим АЧХ CIC-фильтра:

(4)

(4)

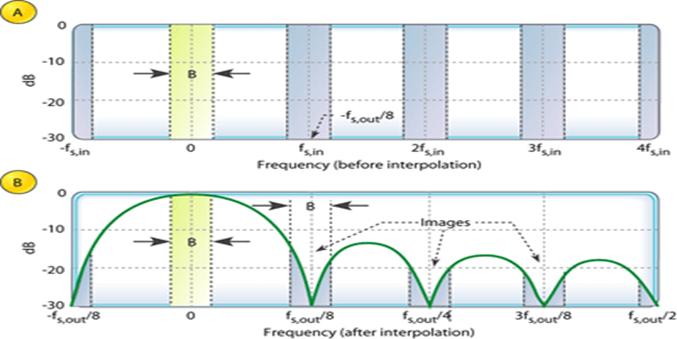

АЧХ

фильтра при коэффициенте интерполяции R=8 на рисунке 5. Как видно из рисунка

наибольшее подавление АЧХ достигается в областях расположения зеркальных

изображений исходного спектра. Однако, для достижения необходимого SFDR может

быть не достаточно одной АЧХ такого вида.

Для решения этой проблемы можно

повысить порядок CIC-фильтра. С увеличением порядка фильтра растет

неравномерность характеристики в полезной области[7]. Для компенсации

неравномерности используют ICIC-фильтр, который имеет обратную характеристику

по сравнению с CIC-фильтром.

рис.

5. АЧХ CIC-фильтра при R=8

Так же процедуру интерполяции можно

оптимизировать переносом блока вставки нулей I. Исходя из линейности

интеграторов и гребенчатых фильтров, можно разместить I перед интеграторами

(рисунок 6).

рис.

6. Оптимизированная структура CIC-фильтра

Для реализации блока вставки

нулей используется программируемый

делитель частоты. Счетчик делителя реализован на основе циклического счетчика

Джонсона с предварительной загрузкой. Преимущество этого счетчика в том, что

при сбивании кода или отсутствии начальной инициализации происходит

самовосстановление. Архитектура делителя взята из [10].

Исходный HDL-код CIC-фильтра получен в

пакете MATLAB SIMULINK. Как правило, вставка нулей в интерполирующих фильтрах

происходит за счет мультиплексора, на

управляющий вход которого подан сигнал делителя частоты. Однако, для

интегратора ситуация, когда на его входе за несколько тактов лишь однажды

ненулевое значение и ситуация, когда

вместо нескольких тактов один со значением на входе, являются эквивалентными. В

силу этого, можно не использовать мультиплексор между гребенчатыми фильтрами и

интеграторами (в месте вставки нулей. См. рисунок 6). Для этого необходимо

первый сумматор секции интеграторов тактировать пониженной частотой входного

потока.

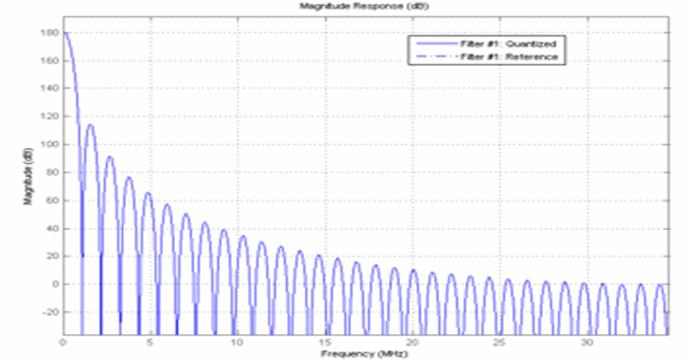

На рисунке 7 представлена АЧХ при

моделировании в MATLAB.

рис.

7. АЧХ после моделирования CIC- фильтра. R=63, N=3

Таким образом, мы не только исключили

мультиплексор из схемы, но и понизили

потребление первого интегратора.

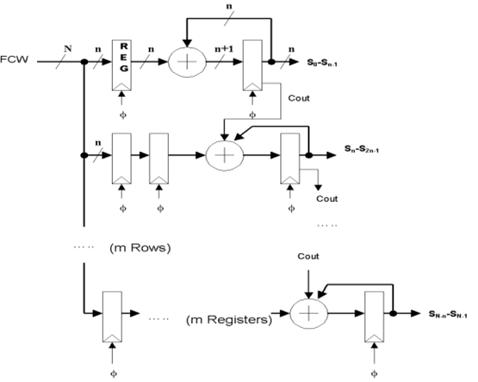

Рассмотрим оптимизацию быстродействия.

Наиболее оптимальным и надежным способом повышения быстродействия сумматора

является его конвейерная структура (рисунок 8). Однако, даже при n=1

быстродейсвие одноразрядного сумматора не дает достаточного запаса по времени.

Для улучшения быстродействия

непосредственно сумматор подвергается конвейеризации. Реализоать конвейеризацию

прямым путем нельзя т.к. дополнительная

задержка S(n-1) на такт приведет к неправильному результату.

рис.

8. Конвейерная структура аккумулятора

Т.е. сигнал обратной связи в сумматоре

всегда должен приходить на выходной триггер без последовательной задержки. Для

решения этой проблемы преобразуем

выражение суммы одноразрядного сумматора:

![]() (5)

(5)

где A – входной бит текущего разряда

S(n-1) – значение суммы на предыдущем

такте

С – перенос с предыдущего разряда

Здесь, операция логического «ИЛИ»

между S и С перенесена ко входу выходного триггера.

При конвейерной реализации увеличение

быстродействие ведет к увеличению потребления СБИС. Если учесть что потребление схемы пропорционально величине f*N (где

f-частота переключений, N-чило триггеров работающих на частоте f), то для

динамического потребления CIC-фильтра имеем:

![]() (6)

(6)

где

Nc – общее число триггеров в

гребенчатой секции;

N1int – число триггеров в первом

интергаторе;

Nint – общее число триггеров всех

интеграторов за вычетом первого.

fin - частота входного потока;

fout – частота выходного

интерполированого потока.

Процедура оптимизации потребления

заключается в следующих рассуждениях. Т.к. СIC-фильтр обладает усилением равным

R(для случая N=1), для сохранения точности выходной поток должен быть

представлен более высокоразрядным словом. Однако, в большинстве систем

обработки сигнала стараются не изменять разрядность сигнала после обработки.

Вследствие этого, на выходе последнего интегратора ставится мультиплексор,

выбирающий в данном случае 14 разрядов из 32 в зависимости от R(чем выше R, тем

выше эти 14 разрядов расположены). Остальные же 18 разрядов становятся

незначимыми. Однако, продолжают работать, а значит потреблять энергию. Для решения этой проблемы можно использовать

технику «clock gating» при синтезе схемы в Design Compiler. Для этого

необходимо использовать триггеры с сигналом разрешения работы. Всего таких

сигналов будет 32(на каждый разряд по 1). Процедура разрешения работы будет

аналогична процедуре мультиплексирования, т.е. разрешать работу только 14 эффективным

разрядам.

Главным достоинством CIC-фильтров

считается отсутствие каких-либо операций умножения. Однако, при реализации

высокочастотных многоразрядных систем этого становиться недостаточно. Особенно

это актуально в проектах использующих как аналоговые, так и цифровые блоки.

После решения проблемы быстродействия, как правило, встает вопрос решения

проблемы потребления. Одним из способов понижения потребления СБИС является

использование техники «clock gating». В данном случае эта техника эффективна

т.к. не все разряды массивных интеграторов используются при вычислении

выходного интерполированного сигнала.

Проблема быстродействия решается за

счет оптимизации архитектуры интеграторов.

Литература

1.

Kwentus, Z. Jiang, and A.

Willson, Jr., «Application of filter sharpening to cascaded integrator-comb

decimation filters» IEEE Transactions on Signal Processing, vol.45, pp.457-467,

February 1997.

2.

J. F. Kaiser and R W.

Hamming, «Sharpening the response of a symmetric nonrecursive filter» IEEE

Transactions on Acoustics, Speech, and Signal Processing, vol. ASSP-25,

pp.415-422, October 1977.

3.

S.J. Orfanidis,

«Introduction to Signal Processing». Upper Saddle River, NJ: Prentice Hall,

1996.

4.

Y. Jang and S. Yang,

“Non-recursive cascaded integrator-comb decimation filters with integer

multiple factors,” in Proc. 44th IEEE Midwest Symp. Circuits and Systems

(MWSCAS), Dayton, OH.

5. Ричард Лайонс, «Цифровая

обработка сигналов». Перевод с английского. М: Бином – пресс. 2011

6.

Pramod K. Meher, Javier Valls, Tso-Bing Juang, K. Sridharan,

and Koushik Maharatna, «50 Years of CORDIC: Algorithms, Architectures, and

Applications». Member, IEEE

7.

A Technical Tutorial on

Digital Signal Synthesis. Analog Device. 1999

8.

Lakshmi Sri Jyothi

Chimakurthy, «DESIGN OF DIRECT DIGITAL FREQUENCY SYNTHESIZER FOR WIRELESS

APPLICATIONS». Auburn, Alabama August 8, 2005

9. Ридико Л. И., «DDS: прямой цифровой синтез

частоты». http://hamradio.tomsk.ru

10. А.В. Корнюхин, М.В.

Старилов, «Выбор оптимального делителя тактовой частоты». Материалы

Международной научно-технической конференции, – 7 декабря 2012 г.МОСКВА.

11. AD9957-1. Datasheet. Analog

Device.