Разработка

маршрута проектирования микросхем DC-DC преобразователей

А.В.

Глухов,

нач.

констр бюро,

ОАО «НЗПП с ОКБ», г. Новосибирск

В.И.

Сединин,

зав.

каф. САПР, д.т.н., проф., sedvi@bk.ru

Л.Г.

Рогулина,

проф.

каф. РТУ, к.т.н, epus206@sibsutis.ru

СибГУТИ, г. Новосибирск

Введение

Создание современной

компонентной базы для альтернативных источников энергии отвечает актуальным задачам повышения эффективности и снижения

потребления электроэнергии от вторичных

источников электропитания. Сложность решения конструкторских и производственных задач заключается в том, что

при бурном развитии микро- и наноэлектроники

значительно возросла плотность компоновки элементов на кристалле, что привело к

безальтернативности применения систем автоматизированного проектирования (САПР)

при разработках больших интегральных схем (БИС). Варьирование электрических

характеристик компонентов (транзисторов) значительно увеличивает время

проектирования БИС и, следовательно, стоимость изделий. Автоматизированное

проектирование позволяет существенно сократить временные и финансовые затраты

на разработку большинства БИС, повышая точность расчётов и сокращая объём

экспериментальных исследований. Продуктивное

использование современного прикладного программного обеспечения

позволяет быстро и адекватно

моделировать процессы, протекающие в БИС, оптимизировать

схемотехнические решения и проверить их работоспособность

при внешних воздействиях ещё на этапах проектирования.

Снижение энергоёмкости, обеспечение надёжности и бездефектности гибридных

компоновочных узлов БИС являются сложными задачами, а процесс их производства

требует постоянного совершенствования. Из-за высокой функциональной сложности

решение этих задач возможно только посредством использования различных методов

автоматизации процессов проектирования на основе мощной вычислительной базы.

Моделирование процессов на всех стадиях

изготовления БИС поддерживается соответствующими программными продуктами,

такими как: OrCAD, MAX+PLUS II, MATLAB,

TCAD

и т.д., а процесс проектирования является

многоуровневым, где каждый уровень характеризуется своим математическим

обеспечением, используемым для моделирования и анализа разрабатываемых схем.

Однако при использовании таких программных средств возникает

проблема, ограничивающая их применение из–за отсутствия достоверных SPICE-моделей

отечественных полупроводниковых приборов и ограниченности средств тестирования

полученных БИС. Для решения этой проблемы необходима разработка отечественных

полупроводниковых компонентов и устройств на их основе, что служит основой производства современных БИС. Ряд вопросов,

связанных с оценкой эксплуатационных характеристик, отладкой

производственных цепочек,

прогнозированием скрытых дефектов БИС, не достаточно глубоко исследован и

является предметом постоянного внимания схемотехников, конструкторов и

технологов. Требуется принципиально новый, комплексный подход к процессу

проектирования, изготовления и тестирования БИС на всех его этапах. Это

особенно важно для БИС, работающих в условиях спецвоздействий, например,

радиации. Поэтому разработка маршрута проектирования БИС предусматривает

создание совокупности математических, имитационных моделей и исследование их динамических характеристик,

используя новые подходы к разработке подсистем функционального и конструкторско-технологического

проектирования.

Таким образом, разумное сочетание имитационного и приборно-технологического

моделирования позволит максимально достоверно оценить

технико-экономические характеристики БИС и решить проблему

реального производства –

сохранение высокого процента выхода годной продукции при уменьшении

топологических размеров и повышении сложности изделий, а также сократить время

на запуск в производство посредством предварительной оптимизации конструкции и

отладки технологических процессов.

Выбор

маршрута проектирования БИС

На

основании проведенного анализа существующих САПР БИС

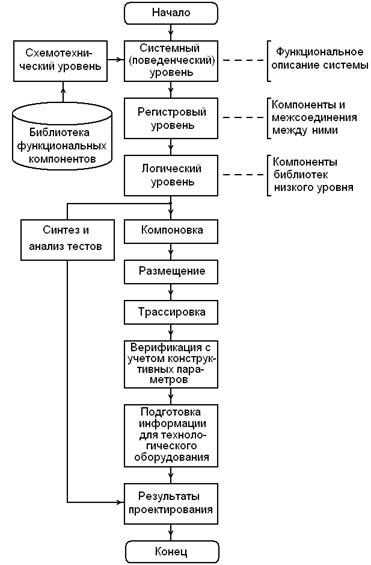

намечена последовательность проектных процедур на маршруте проектирования БИС,

представленная на рисунке 1.

Маршрут проектирования БИС в соответствии с рисунком 1 включает

следующие процедуры:

·

проверка корректности

выбора алгоритма функционирования;

·

формирование

абстрактного описания проекта для составления расписания операций;

·

выбор технологии изготовления и типов

функциональных блоков из имеющихся в библиотеке функциональных компонентов (операционных усилителей,

интеграторов, регистров, сумматоров и т.п.);

·

составление расписания операций (распределение операций по

временным тактам и функциональным блокам) c определением типов операционных блоков

(последовательностные или комбинационные) и исходных данных для синтеза

управляющих блоков;

·

разработка моделей устройств на

регистровом уровне (синтез схем

операционных и управляющих блоков);

·

верификация выбранного

решения;

·

разработка логических схем путём

перевода операционной модели в модель логического (вентильного) уровня с

помощью компиляторов и библиотек

логических элементов;

·

оптимизация и верификация

разработанных логических схем;

·

синтез схем тестирования и тестовых наборов;

·

конструкторско-технологическое проектирование, которое включает в

себя процедуры планирования кристалла, размещения на нем компонентов и

трассировки межсоединений;

·

верификация динамических параметров схемы с учетом задержек в

проведённых межсоединениях;

·

синтез файлов с информацией управления для генераторов

изображений.

рис. 1 Маршрут проектирования БИС

В

известных САПР учёт физических

характеристик (таких как: задержки в элементах и их соединениях и т.д.) осуществляют

на заключительных этапах, где в итерационном цикле проектирования приходится

выполнять дополнительные циклы, что значительно удлиняет время

разработки в случае, когда быстродействие схемы оказывается

неудовлетворительным. Во избежание этого, в работе учитываются физические

характеристики на более ранних этапах на системном уровне, который заключается

в определении ориентировочного взаимного расположения блоков структурной схемы

на кристалле и внешних выводов блоков, что позволяет оценивать длины связей и задержки при

передаче данных уже на ранних стадиях разработки изделия.

К стандартным процедурам

конструкторского проектирования относятся: планирование кристалла, размещение

компонентов и трассировка межсоединений.

В разработанном маршруте проектирования на

функционально-логическом уровне структурного синтеза можно получить не только

работоспособное решение, но и достичь оптимального удовлетворения требований

к быстродействию, рассеиваемой мощности, площади кристалла и тестируемости схемы. Для эффективности

формализации процедур структурного синтеза использовались

специализированные программы, такие как: MULTISIM 10, OrCAD и MATLAB.

Оценка

параметров синтезированных схем и проверка их

работоспособности выполнялась

верификацией (анализом) функциональных и логических схем посредством

программ моделирования, которые ориентированы на системный, регистровый или

логический уровни. Математическое обеспечение

для схемотехнического анализа включает

модели электронных компонентов, методы формирования математических моделей

схем в виде систем обыкновенных дифференциальных уравнений и методы численного

интегрирования систем нелинейных уравнений. Анализ методов моделирования показал, что существует

проблема широкого применения представленных современных

программ схемотехнического моделирования ввиду отсутствия достоверных SPICE-моделей

отечественных полупроводниковых приборов и ограниченность средств

тестирования БИС. Для решения этой

проблемы необходима разработка моделей современных отечественных

компонентов и устройств на их основе для

запуска производства современных БИС. При этом можно использовать зарубежные аналоги, которые

включены в библиотеки программ, а также справочные и/или экспериментальные

данные с помощью которых создаются необходимые

модели (программа Parts-пакет PSpice, Model-система Micro-CAP, PSpice Model Editor-система OrCAD

9.х и т.п.).

Приборно-технологическое

проектирование предназначено для технологического проектирования компонентов

БИС. Оно обеспечивает расчет концентрационных

профилей легирования используемых примесей в вертикальном и горизонтальном

направлениях в двумерной структуре компонентов.

Актуальность проблемы тестирования обусловлена ограниченными управляемостью и наблюдаемостью БИС, так как при десятках-сотнях тысячах транзисторов на кристалле имеется лишь несколько десятков внешних выводов. В цикле проектирования БИС синтез тестов занимают примерно третью часть времени, поэтому решение задачи разработки адекватных моделей для анализа динамических режимов на ранних стадиях проектирования при приемлемой полноте обнаружения константных неисправностей сохраняет постоянную актуальность.

Методика

характеризации сложнофункциональных блоков БИС

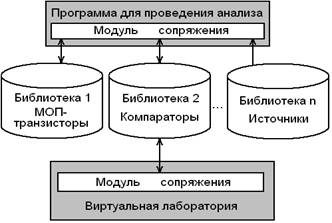

Предложена методика характеризации элементов БИС,

основанная на использовании моделей компонентов из пакета MULTISIM 10,

соответствующих реальным тестовым структурам. Основной частью

данной методики является специально разработанный программный

блок, написанный на языке Си, который

задаёт маршрут и отвечает за подключение, либо отключение функциональных

элементов схемы при проведении анализа, что существенно сокращает затраты на

создание общей схемы (рисунок 2).

рис. 2 Схема взаимодействия модулей

при выполнении анализа

Перед началом характеризации

сценарий, управляющий тестовой схемой, настраивает рабочую

среду САПР, подключая необходимую библиотеку, и задаёт начальные

значения параметров. Далее выполняется минимизация целевой функции:

![]() ,

,

которая включает критерии

оценки качества преобразования электрической энергии (потребляемый ток ![]() , коэффициент полезного действия η, коэффициент

мощности нагрузки

, коэффициент полезного действия η, коэффициент

мощности нагрузки ![]() , действующее значение пульсаций напряжения гармонических составляющих

, действующее значение пульсаций напряжения гармонических составляющих

![]() ) и надёжности (интенсивность отказов λ, срок службы Tсл). Рассчитываются характеристики исследуемого объекта. Сценарий

программы предусматривает изменение

маршрута прохождения сигнала в тестовой схеме для каждой последующей итерации и

изменение параметров исследуемого источника или других элементов схемы. По

полученным результатам автоматически строятся графические зависимости, где отмечаются характерные точки и значения,

что позволяет повысить его информативность. Разработанная методика позволяет

всесторонне исследовать отдельные устройства. При этом процесс оптимизации занимает относительно небольшое время, что

существенно сокращает общие временные затраты на проектирование. Данная

методика позволяет работать с любыми другими аналоговыми блоками после

некоторого изменения сценария.

) и надёжности (интенсивность отказов λ, срок службы Tсл). Рассчитываются характеристики исследуемого объекта. Сценарий

программы предусматривает изменение

маршрута прохождения сигнала в тестовой схеме для каждой последующей итерации и

изменение параметров исследуемого источника или других элементов схемы. По

полученным результатам автоматически строятся графические зависимости, где отмечаются характерные точки и значения,

что позволяет повысить его информативность. Разработанная методика позволяет

всесторонне исследовать отдельные устройства. При этом процесс оптимизации занимает относительно небольшое время, что

существенно сокращает общие временные затраты на проектирование. Данная

методика позволяет работать с любыми другими аналоговыми блоками после

некоторого изменения сценария.

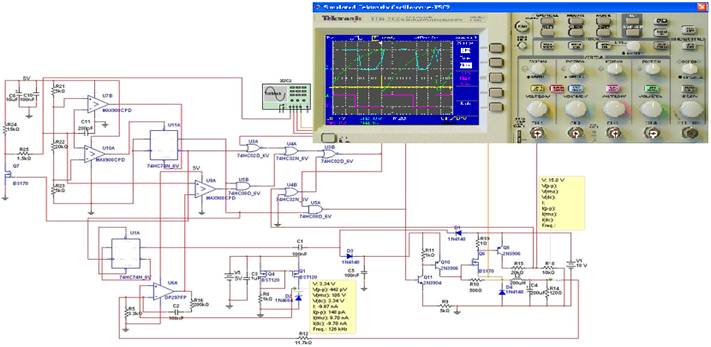

В результате проведения такой структурно – параметрической оптимизации на этапе схемотехнического

проектирования получены оптимальные принципиальные схемы отдельных блоков БИС

и проведено моделирование полной принципиальной схемы. На рисунке 3

представлена электрическая схема источника положительного напряжения и

временные диаграммы его работы.

рис.3 Электрическая схема модели источника положительного напряжения и временные диаграммы работы

В процессе выполнения структурно

– параметрической оптимизации DC-DC преобразователя проводилась минимизация

потерь, потребляемого тока при

варьировании параметрами транзисторов и реактивных элементов, а также

структур основных блоков. Во всём рабочем диапазоне мощностей (PН) с учетом

отклонений входного напряжения (Uвх) осуществлена проверка характеристик преобразователя постоянного напряжения. В

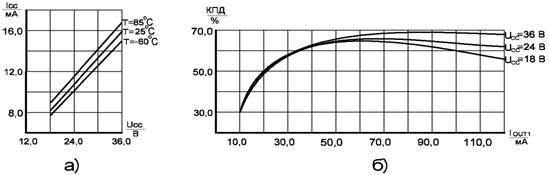

качестве примера приведены следующие зависимости: статического тока потребления IСС от входного напряжения UСС и температуры T (рисунок 4 а); КПД от тока нагрузки IOUT1 и входного напряжения UCC (4 б).

рис. 4 Зависимости: статического тока

потребления IСС от входного напряжения UСС и температуры T (а); КПД от тока

нагрузки IOUT1

и входного напряжения UCC

Из представленных

графических зависимостей следует, что основным достоинством разработанной БИС

является широкий диапазон входных напряжений, малый потребляемый ток, что

подразумевает более высокий КПД и позволяет расширить область её применения.

Маршруты

технологического процесса изготовления БИС

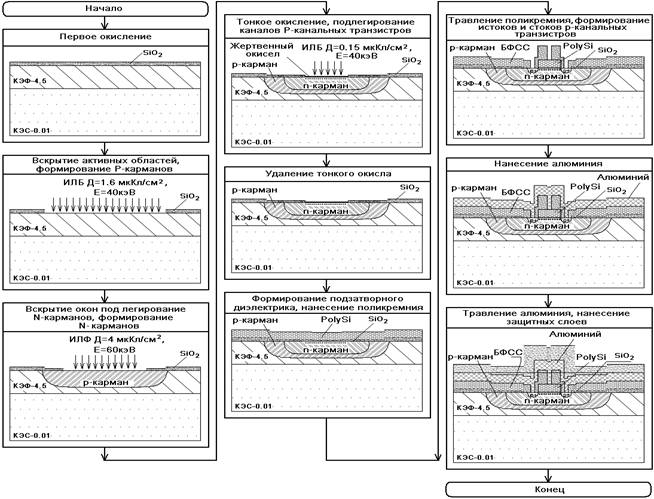

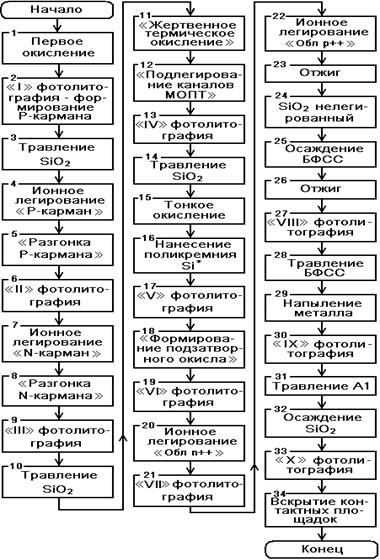

Разработан перспективный технологический

маршрут, особенностью которого является

возможность внесения поправок в

базовые операции, что позволяет получать уникальные приборы и дает широкие

возможности совершенствования параметров и характеристик полученных БИС.

Кристаллы разработанной схемы управления изготовлены по базовой КМОП-технологии

с кольцевым самосовмещённым поликремниевым затвором. Последовательность операций маршрута приведена

на рисунке 5, где исходным

материалом изготовления

элементов управляющей БИС

служат эпитаксиальные структуры

типа ![]() . Одной из главнейших задач при проектировании данного

технологического маршрута является внедрение технологии формирования «кармана в

кармане», никогда ранее не

применявшейся на предприятии в России.

Для определения параметров новой технологии, применялся САПР TCAD Sentaurus. Технологическая модель

строилась по алгоритму, технологического проектирования в среде TCAD Sentaurus, где

параметры модели вводятся

в подсистеме SProcess. Данное

средство технологического проектирования позволило определить важнейшие

параметры и этапы изготовления элементов БИС, такие как глубины залегания p-n-переходов,

поверхностные концентрации активной примеси в различных областях структуры,

электрофизические параметры как отдельных областей, так и готовых приборов,

входящих в состав БИС.

. Одной из главнейших задач при проектировании данного

технологического маршрута является внедрение технологии формирования «кармана в

кармане», никогда ранее не

применявшейся на предприятии в России.

Для определения параметров новой технологии, применялся САПР TCAD Sentaurus. Технологическая модель

строилась по алгоритму, технологического проектирования в среде TCAD Sentaurus, где

параметры модели вводятся

в подсистеме SProcess. Данное

средство технологического проектирования позволило определить важнейшие

параметры и этапы изготовления элементов БИС, такие как глубины залегания p-n-переходов,

поверхностные концентрации активной примеси в различных областях структуры,

электрофизические параметры как отдельных областей, так и готовых приборов,

входящих в состав БИС.

рис. 5

Технологический маршрут

Для формирования P-канальных транзисторов, с целью обеспечения

необходимых параметров схемы и сохранения параметров мощного силового

транзистора предусмотрено формирование «N-кармана» в «P-кармане». При этом напряжение

пробоя «P- карман» – «подложка»

должно быть не менее UПР = 60 В. Необходимо также обеспечить достаточную глубину залегания

«N-кармана», но не допустить «прошивания» границ «P-кармана» (см. рисунок 6).

рис.6 Этапы формирования типового P-канального транзистора

Результаты

моделирования показали, что при формировании «P-кармана», использование стандартной для КМОП

технологии, дозы ионного легирования

бора Д=1,6 мкКл/см2, при энергии

легирования Е = 40 кэВ,

достаточно для обеспечения напряжения пробоя

«P-карман» - «подложка» более UПР = 60 В. Режим разгонки примеси

разработан на основе стандартного для КМОП технологии режима

разгонки «P-кармана» N-канальных транзисторов, с поправкой на время разгонки,

для обеспечения необходимой глубины залегания кармана. Уточнённое время разгонки составляет 6 ч в инертной

атмосфере.

В ходе работы были смоделированы технологические маршруты изготовления P- и N-канальных транзисторов, получены их двумерные геометрические структуры в среде TCAD Sentaurus и исследованы их особенности. Полученные данные были использованы при подготовке итоговых комплектов фотошаблонов для изготовления транзисторов.

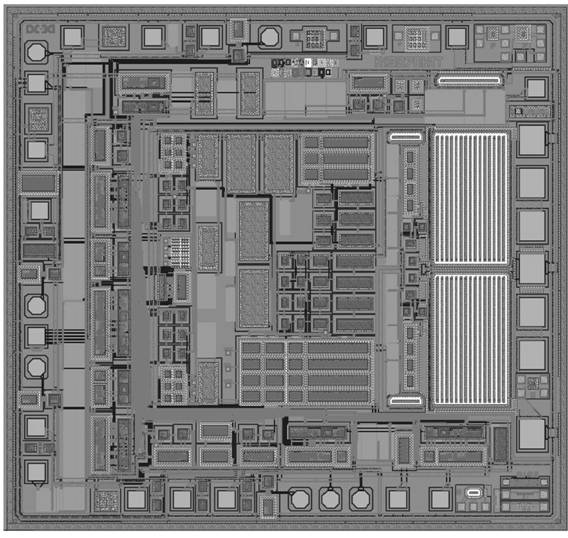

На основе разработанной

принципиальной электрической схемы DC-DC

преобразователя разработана топология кристалла. Основной задачей на этапе

разработки топологии является размещение и трассировка элементов БИС на

кристалле. После размещения, компоновки и трассировки площадь всех библиотечных

элементов заняла около 80 % площади

кристалла, что говорит об оправданности выбранной методики проектирования.

После завершения проектирования

топологии была проведена проверка на

соответствие нормам и «Правилам проектирования

топологии» и верификация топологии на соответствие принципиальной схеме

согласно методике проверки топологических схем с использованием

редактора LayEd. Разработанная топология кристалла микросхемы

представлена на рисунке 7.

рис.7 Топология кристалла микросхемы DC-DC преобразователя

Заключение

В результате

разработки топологии DC-DC

преобразователя получена площадь кристалла 4,6×4,25 мм2 с размещёнными

на ней активными элементами в количестве 864 шт. Предложенные в работе решения,

соответствуют современной тенденции развития методов автоматизированного

проектирования сложных радиоэлектронных схем, их оптимизации на этапах

проектирования, которые направлены на

повышение эффективности и надёжности, так как позволяют выявлять возможные

дефекты на ранних этапах проектирования и устранять их с минимальными

затратами. На основании вышеизложенного можно сделать вывод о возможности

широкого внедрения и применения предложенной автоматизированной системы

схемотехнического и конструкторско-технологического проектирования БИС на

промышленных объектах и в практических разработках.