Тепловой

анализ в задачах размещения компонентов и топологического

планирования печатных плат

В.Е.Шельбах,

инженер-разработчик, vladimir_schellbach@mentor,

Н.И.Филатов

д.т.н., руководитель группы, nicolai_philatov@mentor.com,

Mentor Graphics,

, г.Москва

Увеличение энергопотребления

электронных устройств, и, как следствие, возрастание температуры компонентов

печатных плат, требуют учета этих факторов в процессе проектирования платы (

здесь и далее - PCB, printed circuit board ), в частности,

в задачах размещения и трассировки, а также в задачах электрического

моделирования.

В данной статье мы попытаемся

предложить алгоритмы использования результатов температурного анализа в

процессе проектирования PCB с целью оптимизации распределения температуры по плате

и удовлетворения электро-тепловых ограничений, накладываемых на схему.

1. Смешанное электро-тепловое

моделирование печатных плат

Изменение температуры

компонент PCB оказывает существенное влияние на временные задержки

при распространении сигналов, а также на энергопотребление компонент схемы,

что, в свою очередь, оказывает обратное влияние на распределение температуры.

Соответственно, необходим комплексный подход к моделированию.

Такой

подход предложен, например, в [1] – предлагается единая трехмерная модель для

решения задачи смешанного электро-теплового анализа, основанная на «методе

конечного элемента» ( FEM ). Существуют

коммерческие продукты ( например, [2] ) , реализовавшие такой подход. Этот

подход дает хорошую точность, но, к сожалению, имеет и существенный недостаток

– из-за больших размерностей задачи ( современные PCB могут содержать

более 5000 компонентов и иметь 18-20 трассировочных слоев ) время работы такой

программы становится очень большим, и может исчисляться сутками. Это может быть

приемлемо на этапе финальной верификации платы, но совершенно недопустимо на

этапах проектирования, когда дизайнер PCB

выполняет процедуры размещения и трассировки и периодически хочет сделать

быструю оценку электро-тепловых свойств.

Для решения такой задачи

предлагается компромиссный вариант – вместо полного моделирования выполняется

как бы «одна итерация» цикла электро-теплового анализа, т.е., сначала делается

температурный анализ, принимающий на вход номинальные электрические характеристики

схемы, затем выполняется электрический анализ ( расчет задержек в сигнальных

трассах, распределения напряжения в цепях земли/питания и т.д. ), который

учитывает распределение температуры по трассам и, в соответствии с этим, делает

перерасчет величин сопротивлений, а затем, вновь делается температурный анализ,

который использует полученное распределение плотностей токов в электрических

цепях а так же, используя некоторые эмпирические модели, учитывает зависимость

энергопотребления компонент от локальной температуры.

Предложенный подход дает

возможность учесть взаимозависимость теплового и электрического анализа «в первом

приближении», что, как показывают численные эксперименты, дает вполне

приемлемую точность, и позволяет сократить время работы программы в десятки

раз.

2. Задача thermal-driven placement and floorplanning

Одним из инструментов оптимизации

температурного распределения по плате является оптимизация размещения. Стоит отметить,

что задача оптимизации температуры для PCB несколько сложнее, чем та же задача для интегральной

схемы, которая находится внутри корпуса и соответственно, переразмещение не

оказывает существенного влияния на окружающий воздух и поэтому достаточно

добиваться равномерности распределения источников тепла по площади схемы ( см., например [3] ). Существуют следующие способы воздействия на

распределение температур путем переразмещения компонентов:

-

Запрещать

установку компонент с жесткими

температурными ограничениями близко к сильным источникам тепла;

-

Не размещать

«высокие» компоненты вверх по потоку набегающего воздуха, что вызовет

«блокировку» других компонентов вниз по потоку, и как следствие, ухудшение

теплообмена с окружающим воздухом;

Учет данных эффектов

позволяет добиться существенного понижения температуры «критических»

компонентов и выполнить температурные и электрические ограничения

функционирования схемы. Разумеется, при этом должны учитываться и требования по

выдерживанию временных ограничений, а так же трассируемости PCB. Некоторые результаты приведены ниже.

3. Влияние топологических

параметров схемы на температурное поле печатной платы

Данные о топологии PCB (

размещение компонентов, а так же структура всех слоев и трассировка цепей ) оказывают

очень существенное влияние на результаты теплового анализа. Заметим, что

информация о трассировке очень важна, т.к. коэффициент теплопроводности металла

отличается от диэлектрика в несколько сотен раз. Неточное задание разводки

платы и геометрии слоёв питания ведёт к неверному результату при решении уравнения

теплопроводности.

Приведем пример для

тестовой платы. Температурный анализ выполнялся перед процедурой трассировки и

после.

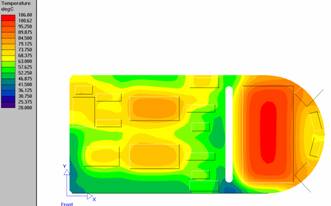

Температурная карта до

трассировки:

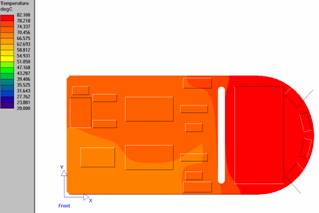

После:

После:

Отметим,

что алгоритмы трассировки должны принимать во внимание распределение плотностей

токов в металле и изменять геометрию проводников в соответствии с ограничениями

по токам в трассах.

4. Результаты

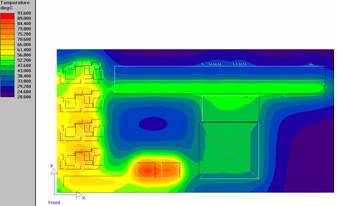

Здесь мы хотели бы привести

результаты оптимизации размещения для тестовой платы с целью минимизации

пиковой температуры ( предполагалось, что все компоненты имеют одинаковые

температурные ограничения ).

До оптимизации:

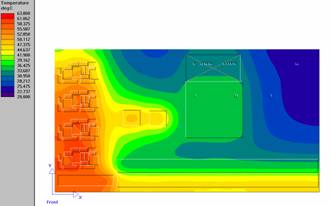

После:

После:

Как видно, значение пиковой температуры уменьшилось с

93 то 63 градусов.

Литература

1.

Finite element analysis of a SWEAT structure with a

3-D, nonlinear, coupled thermal-electric model. Dion, M.J.; Proceedings of

the 1992 International Conference on 16-19 March 1992 Page(s):12 – 17

2.

Ansoft, Coupled Thermal and Stress

Analysis for Electromagnetic Applications, http://www.ansoft.com/products/tools/ephysics/features.cfm

3.

Thermal Driven Module Placement Using Sequence-pair.

Okada, N.; Kodama, C.; Sato, T.;

Fujiyoshi, K.; Circuits and Systems, 2006. APCCAS 2006. IEEE

Asia Pacific Conference on 4-7 Dec. 2006 Page(s):1871 - 1874